Modul IV

Laporan Akhir 1

2. Alat dan Bahan

[Kembali]

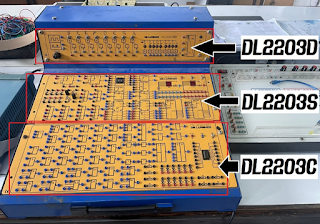

1. Panel DL 2203D

2. Panel DL 2203C

3. Panel DL 2203S

4. Jumper

5. IC 74111

Kelebihan JK Flip-flop adalah tidak adanya kondisi terlarang atau yang berarti di beri berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluarannya / outputnya. berikut adalah symbol dan tabel kebenaran dari JK Flip-Flop.

Pada percobaan 1 ini dirangkai suatu rangkaian Shift Register (register geser) jenis SISO keluaran output 4 bit dengan perwakilan output logicprobe. Pada rangkaian shift register SISO keluaran 4 bit berarti menggunakan 4 buah IC J-K flip flop sebagai perwakilan 1 bit keluaran untuk 1 buah J-K flipflop.

Pada rangkaian ini merupakan rangkaian SISO yang berarti memiiki 1 input masukan dari J-K flip flop pertama dan 1 input keluaran dari J-K flip flop terakhir (ke-4) dimana angka akan bergeser dari bit pertama keluaran hingga bit ke-4 keluaran setiap inputan logika baru yang diinputkan pada inputan IC J-K flip flop pertama, berarti pada rangkaian terjadi perwakilan dari penggeseran masukan suatu biner ke kiri atau ke kanan dimana pergeseran ini akan mewakili MSB dan LSB dari 4 bit binner keluaran. Terjadinya pergeseran input masukan logika pada rangkaian ini juga berarti bahwa proses terjadinya register geser ini dapat menyimpan memori sementara pada saat pergeseran masukan menuju keluaran bit ke-4 dari dearah lingkup keluaran 4 bit.

Proses kerja rangkaian ini yaitu pada input D-flip flop dari input J dan K akan dikendalikan oleh switch yang berarti input akan dikendalikan sesuai pengaturan switch baik itu input logika 1 terhubung power maupun berlogika 0 terhubung ground, saat input D flip flop diberi masukan logika 1 atau 0, lalu input clock secara serempak aktif high, maka output akan memproses terjadi operasi set (jika input logika 1) atau memproses terjadi operasi reset (jika input logika 1) sehingga diperoleh output Q pada J-K flip flop pertama, lalu pada output J-K flip flop berikutnya dengan input clock aktif high secara serempak dan juga dipengaruhi input J-K flip flop sebelumnya akan membacanya sehingga dengan delay sesuai kondisi input clock (delay pada fall time) sehingga output akan bergeser menyimpan memori sementara dari masukan bit pertama hingga ke-4 dimana bit ke-4 merupakan tumpuan kepastian dari keluaran pergeseran input yang menandakan bahwa pergeseran input terjadi sesuai prinsip kerja dari SISO yaitu 1 masukan yang bergeser menuju 1 keluaran.

6. Analisa [Kembali]

1. Analisa output yang dihasilkan tiap tiap kondisI

Jawab:

-Kondisi 1: B3-B6 = 0

B0,B2 = 1

B1 = x

Pada kondisi ini switch B3-B6 diberi logika 0, dan B0,B2 diberi logika 1, dan B1 diberi tanda x, yang mana x itu sebagai operational berjalannya rangkaian dan ketika dijalankan terlihat data yang kita masukkan satu persatu dan juga keluar satu persatu atau data mengalami pergeseran. Sehingga dapat kita simpulkan bahwa ini merupakan serial in serial out (SISO)

-Kondisi 2: B3-B6 = 0

B1 = x

B0 = 1

B1,B2 = 0

Pada kondisi ini switch B3-B6 diberi logika 0, dan B0 diberi logika 1, B1 diberi tanda x yang nantinya sebagai operational berjalannya rangkaian, B2 = ⬇️, maksudnya kondisinya 1 ke 0, dan ketika dijalankan tampak terlihat datanya masuk satu persatu dan data keluar secara serentak. Sehingga dapat kita simpulkan bahwa ini merupakan serial in paralel out (SIPO)

-Kondisi 3: B3-B6 = x

B1 = 0

B0,B2 = 1

Pada percobaan ini switch B0-B6 diberi tanda x, yang nantinya sebagai operational berjalnnya rangkaian, B1 diberi logika 0, dan B0,B2 diberi logika 1. Ketika dijalankan tampak terlihat bahwa data yang masuk secara serentak dan data yang keluar secara satu persatu. Sehingga dapat kita simpulkan bahwa ini paralel in serial out (PISO)

-Kondisi 4: B3-B6 = x

B0 = 1

B1,B2 = 0

Pada percobaan ini switch B3-B6 diberi tanda x, yang nantinya sebagai operational berjalannya rangkaian, dan B0 diberi logika 1, dan B1,B2 diberi logika 0. Ketika rangkaian dijalankan tampak terlihat bahwa data yanng masuk dan keluar itu secara serentak, dapat disimpulkan bahwa ini paralel in paralel out (PIPO)

2. Jika gerbang and pada rangkaian dihapus, sumber clock dihubungkan langung ke flip-flop, bandingkan output yang didapatkan

Jawab:

Output yang didapatkan sama saja, karena gerbang and terhubung dengan L masukkan, switch B2 dan komponen clock pad rangkaian, dan keluaran dihubungkan pada tiap tiap flip-flop sehingga pengaruhnya tidak mempengaruhi hasil output yang didapat

Download html Klik disini

Download Video percobaan Klik disini

Download File Rangkaian Klik disini

Dataheet AND gate klik disini

Download datasheet D Flip-Flop: Klik disini

Download datasheet saklar SW-SPDT: Klik disini

Download datasheet IC 74LS47 Klik disini

Download datasheet IC 74LS90 Klik disini

Datasheet 7493 Klik disini

Download datasheet 7-segment Klik disini

Datasheet LED Klik disini

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.png)

Tidak ada komentar:

Posting Komentar